- 您现在的位置:买卖IC网 > Sheet目录1917 > DSPIC30F3013-20I/ML (Microchip Technology)IC DSPIC MCU/DSP 24K 44QFN

2010 Microchip Technology Inc.

DS70139G-page 69

dsPIC30F2011/2012/3012/3013

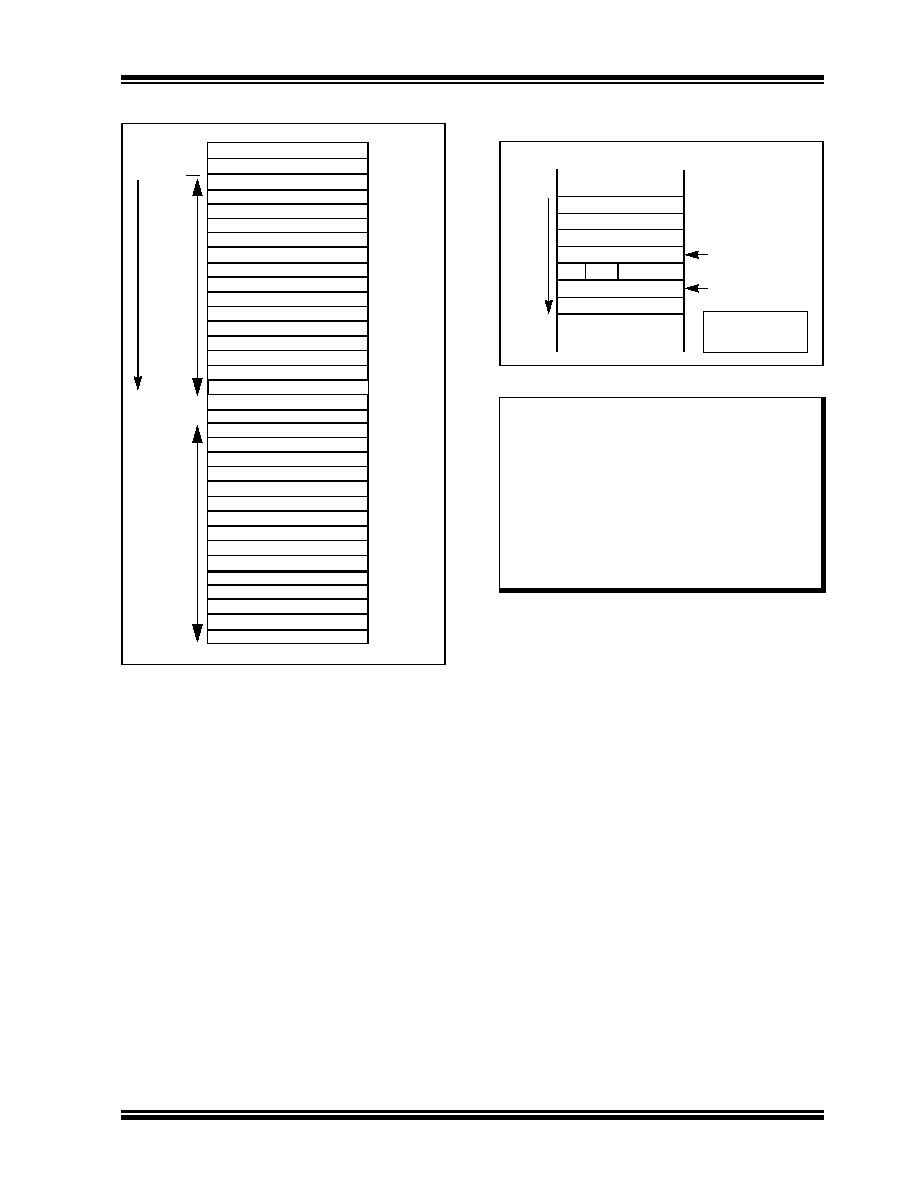

FIGURE 8-1:

TRAP VECTORS

8.4

Interrupt Sequence

All interrupt event flags are sampled in the beginning of

each instruction cycle by the IFSx registers. A pending

Interrupt Request (IRQ) is indicated by the flag bit

being equal to a ‘1’ in an IFSx register. The IRQ causes

an interrupt to occur if the corresponding bit in the

Interrupt Enable (IECx) register is set. For the

remainder of the instruction cycle, the priorities of all

pending interrupt requests are evaluated.

If there is a pending IRQ with a priority level greater

than the current processor priority level in the IPL bits,

the processor is interrupted.

The processor then stacks the current program counter

and the low byte of the processor STATUS register

(SRL), as shown in Figure 8-2. The low byte of the

STATUS register contains the processor priority level at

the time prior to the beginning of the interrupt cycle.

The processor then loads the priority level for this

interrupt into the STATUS register. This action disables

all lower priority interrupts until the completion of the

Interrupt Service Routine (ISR).

FIGURE 8-2:

INTERRUPT STACK

FRAME

The RETFIE (return from interrupt) instruction unstacks

the program counter and STATUS registers to return

the processor to its state prior to the interrupt

sequence.

8.5

Alternate Vector Table

In program memory, the Interrupt Vector Table (IVT) is

followed by the Alternate Interrupt Vector Table (AIVT),

as shown in Figure 8-1. Access to the alternate vector

table is provided by the ALTIVT bit in the INTCON2

register. If the ALTIVT bit is set, all interrupt and

exception processes use the alternate vectors instead

of the default vectors. The alternate vectors are

organized in the same manner as the default vectors.

The AIVT supports emulation and debugging efforts by

providing a means to switch between an application

and a support environment without requiring the

interrupt vectors to be reprogrammed. This feature also

enables switching between applications for evaluation

of different software algorithms at run time.

If the AIVT is not required, the program memory

allocated to the AIVT may be used for other purposes.

AIVT is not a protected section and may be freely

programmed by the user.

Address Error Trap Vector

Oscillator Fail Trap Vector

Stack Error Trap Vector

Reserved Vector

Math Error Trap Vector

Reserved

Oscillator Fail Trap Vector

Address Error Trap Vector

Reserved Vector

Interrupt 0 Vector

Interrupt 1 Vector

—

Interrupt 52 Vector

Interrupt 53 Vector

Math Error Trap Vector

D

e

cr

easing

Pr

iorit

y

0x000000

0x000014

Reserved

Stack Error Trap Vector

Reserved Vector

Interrupt 0 Vector

Interrupt 1 Vector

—

Interrupt 52 Vector

Interrupt 53 Vector

IVT

AIVT

0x000080

0x00007E

0x0000FE

Reserved

0x000094

Reset - GOTO Instruction

Reset - GOTO Address

0x000002

Reserved

0x000082

0x000084

0x000004

Reserved Vector

Note 1: The user can always lower the priority

level by writing a new value into SR. The

Interrupt Service Routine must clear the

interrupt flag bits in the IFSx register

before lowering the processor interrupt

priority, in order to avoid recursive

interrupts.

2: The IPL3 bit (CORCON<3>) is always

clear

when

interrupts

are

being

processed. It is set only during execution

of traps.

<Free Word>

0

15

W15 (before CALL)

W15 (after CALL)

S

tack

Gr

ows

T

o

wa

rds

Higher

Addr

ess

0x0000

PC<15:0>

SRL IPL3 PC<22:16>

POP : [--W15]

PUSH : [W15++]

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

DSPIC30F4011-30I/ML

IC DSPIC MCU/DSP 48K 44QFN

DSPIC30F4013-30I/ML

IC DSPIC MCU/DSP 48K 44QFN

DSPIC30F5013-30I/PT

IC DSPIC MCU/DSP 66K 80TQFP

DSPIC30F5015-30I/PT

IC DSPIC MCU/DSP 66K 64TQFP

DSPIC30F6010-20E/PF

IC DSPIC MCU/DSP 144K 80TQFP

DSPIC30F6010A-30I/PF

IC DSPIC MCU/DSP 144K 80TQFP

DSPIC30F6013A-30I/PF

IC DSPIC MCU/DSP 132K 80TQFP

DSPIC30F6014-30I/PF

IC DSPIC MCU/DSP 144K 80TQFP

相关代理商/技术参数

dsPIC30F3013-20I/SO

功能描述:数字信号处理器和控制器 - DSP, DSC 28LD 20MIPS 24 KB RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT

dsPIC30F3013-20I/SP

功能描述:数字信号处理器和控制器 - DSP, DSC 28LD 20MIPS 24 KB RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT

DSPIC30F3013-30I/ML

功能描述:数字信号处理器和控制器 - DSP, DSC Sensor RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT

DSPIC30F3013-30I/SO

功能描述:数字信号处理器和控制器 - DSP, DSC Sensor RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT

DSPIC30F3013-30I/SO

制造商:Microchip Technology Inc 功能描述:IC DSC 16BIT 24KB 40MHZ 5.5V SOIC-28

DSPIC30F3013-30I/SP

功能描述:数字信号处理器和控制器 - DSP, DSC Sensor RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT

DSPIC30F3013-30I/SP

制造商:Microchip Technology Inc 功能描述:16-Bit Digital Signal Controller

dsPIC30F3013T-20E/ML

功能描述:数字信号处理器和控制器 - DSP, DSC 44LD 20MIPS 24 KB RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT